Hardware Architecture

This project relies on next-generation FPGA to process Ethernet frames at line-rate without host CPU intervention.

FPGA Core

Optimized programmable logic.

- VHDL Pipeline

- Ultra-fast RAM

- Full Offloading

Interfaces QSFP+

High-speed connectivity.

- Standard 40GbE

- Low BER

- Fiber Support

Performance Objectives

40 Gb/s

Constant Throughput

< 1 μs

Processing Latency

0%

Host CPU Load

Development Log

19 Mar 2026

Recherche

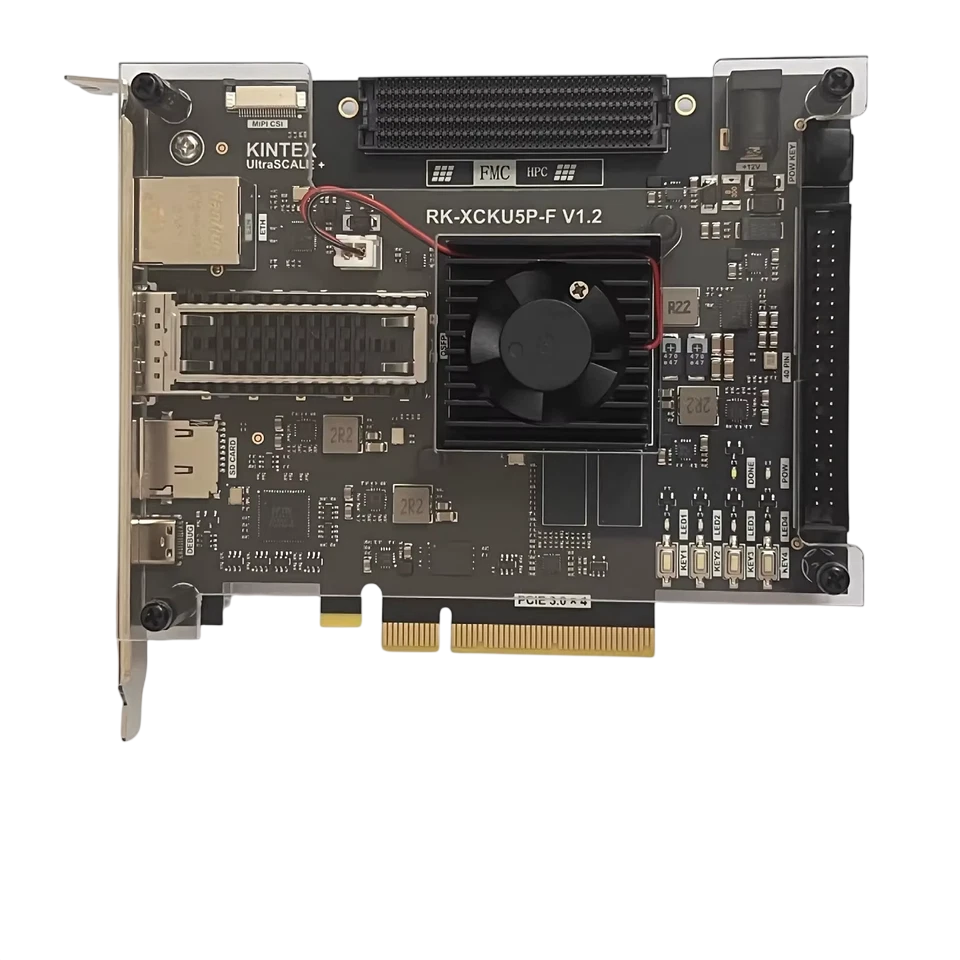

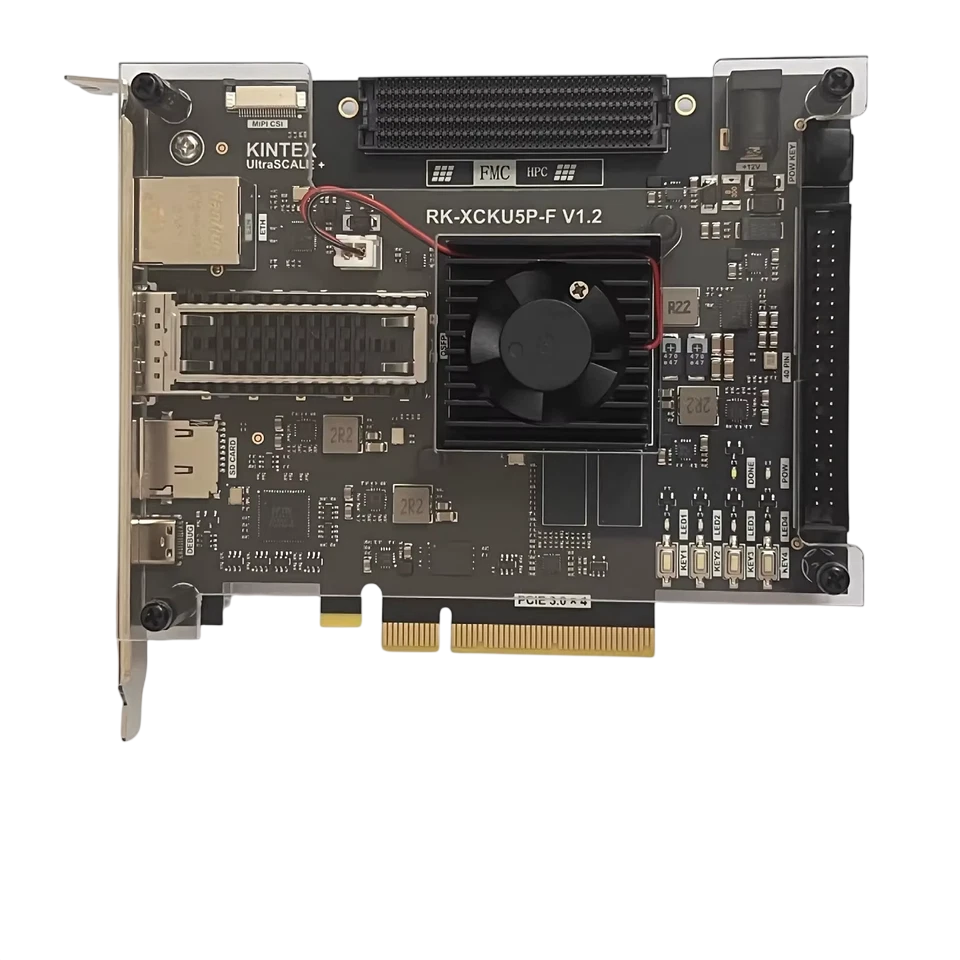

Hardware Choice: KU5P FPGA & Vivado

After evaluating several chips, I selected the KU5P (XCKU5P) development board for its unbeatable price-to-performance ratio. Its wide range of connectors (QSFP28 100G, FMC HPC, PCIe 3.0) ensures great modularity and easy future upgrades. Additionally, it is fully compatible with Vivado, the industry-standard tool we use at school, making development and integration seamless.